主な研究テーマ

本研究室では,VLSIと呼ばれる集積回路技術に関する研究を行っています.マイクロプロセッサやシステムオンチップ(SoC)などの高性能ロジックシステムや,ウェアラブルデバイスなどに搭載される低電圧ロジックシステムに用いるメモリ技術を中心とした新しい低消費エネルギー/高エネルギー効率CMOS技術の研究・開発を行っています.また,将来のより高性能なVLSIを実現するために有用となる新概念の高性能トランジスタ技術,ウェアラブルデバイスへの電力供給源として,人体から放出される熱によって発電を行う熱電発電技術なども研究・開発を進めています.1.不揮発記憶を用いた低消費エネルギー/高エネルギー効率CMOS技術

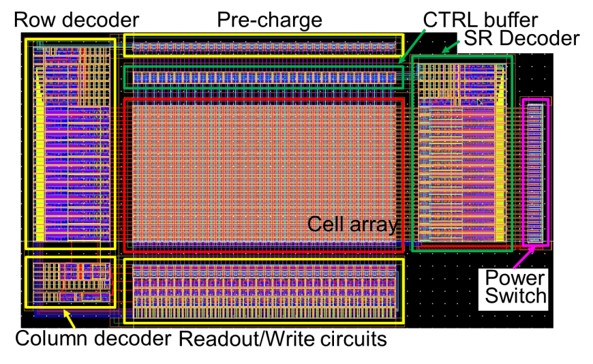

近年のコンピューティング・システムに搭載されているマイクロプロセッサや,スマートフォンなどに搭載されているシステム・オン・チップ(SoC)では,トランジスタのリーク(漏れ)電流によって待機時に消費する電力(待機時電力)が著しく大きく,その削減が重要な課題となっています.何も対策を講じなければ,この待機時電力は演算処理を行っているときの電力と同レベルとなるとても大きなもので,マイクロプロセッサやSoCの性能を左右する重要な要因の1つになっています.現在のCMOSロジックではパワーゲーティング(PG)と呼ばれる電源遮断による待機時電力の削減方法を導入していますが,CMOSロジックシステム内にある記憶回路が揮発性のため(電源遮断するとデータが消失する),その削減効率は制約を受けてしまいます.本研究室では,情報の不揮発記憶を利用して,このような待機時電力を効率よく削減する技術を開発しています.不揮発性メモリ素子とCMOS回路を融合させることでSRAMやフリップフロップ(FF)といった記憶回路を不揮発化した不揮発性SRAM,不揮発性FFといった記憶回路と,これらを用いて実現できる不揮発性パワーゲーティング(NVPG)という新しいアーキテクチャを用いて,無駄なエネルギー消費を最大限に削除できるCMOSロジックシステムの実現を目指しています.

2.擬似不揮発記憶を用いた低消費エネルギー/高エネルギー効率CMOS技術

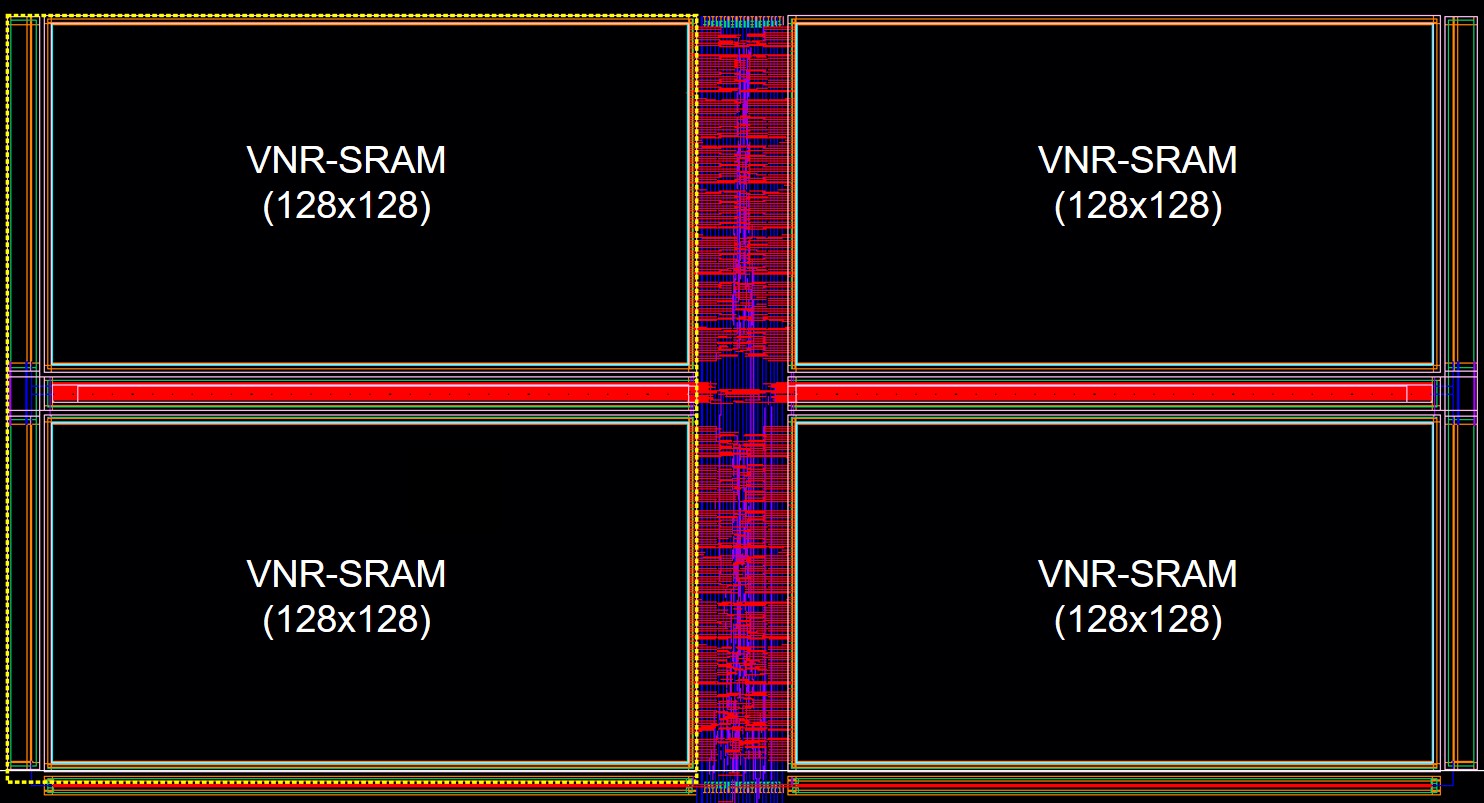

従来のロジックシステムにおけるパワーゲーティング(PG)では,ロジックシステムをブロック(パワードメインと呼ばれます)に分割して,このブロックが未使用時には電力供給を遮断することによって待機時電力の削減を実現しています.回路ブロックはパワースイッチと呼ばれるトランジスタによって電源遮断されますが,このとき回路ブロックには微小な電圧が残っています.この非常に小さな電圧(超低電圧)で記憶回路の情報を保持することができれば,これは実質的に不揮発記憶とみなすことができます(擬似不揮発記憶).本研究室ではこのような擬似不揮発記憶を用いたPGと,この実現に必要となる擬似不揮発性SRAM,擬似不揮発性FFといった記憶回路を提案し,研究・開発を進めています.これらの記憶回路はCMOSのみで構成され,通常の電圧下では高速に動作し,超低電圧ではデータを失うことなく保持できる擬似不揮発記憶が可能です.擬似不揮発記憶をCMOSロジックシステムに用いれば,不揮発記憶を用いたときに匹敵するくらいの高い待機時電力削減効果が得られると予想しています.

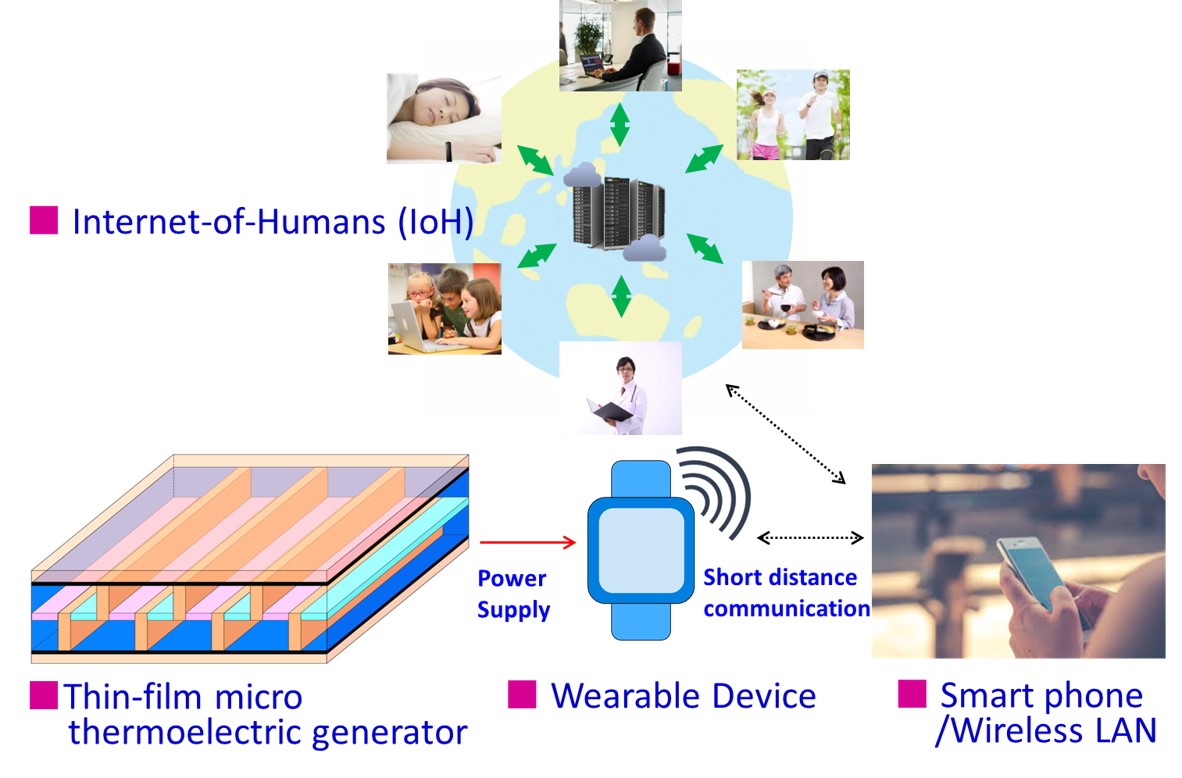

3.薄膜熱電発電モジュール(ウェアラブルデバイス応用)

近年,医療・介護・ヘルスケアを対象としたInternet of Humans (IoH) が注目を集めています.これはヒトを対象としたIoTとも言えるものです.ウェアラブルデバイス(WD)はこのようなIoHにおけるMan-Machine Interfaceとして期待されています.このようなWDの機能のうち,消費電力の大きなものは無線通信ですが,スマートフォンや室内中継器などとの併用を前提とすれば,WDの無線通信は消費電力の低い短距離に限定することが可能となりますので,ヒトの体温を用いた熱電発電をWDに応用できる可能性があります.本研究室では,WDの電源に応用できる体温を用いた熱電発電モジュールの研究開発を行っています.半導体集積回路(VLSI)に用いられる微細加工技術を用いることで実現できる新型の熱電発電モジュールを提案して,その最適設計や性能解析などを進めています.この技術を用いて,バッテリーを必要としないまたは充電頻度の極めて少ないWDの実現を目指しています.

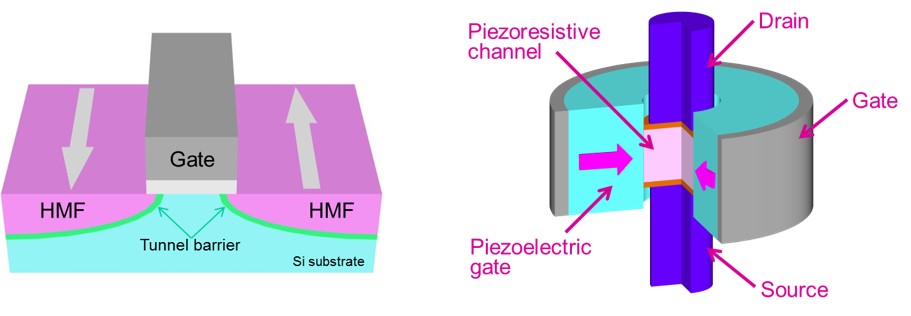

4.新原理高機能・高性能トランジスタ

将来のVLSIに有用な新原理に基づく高機能トランジスタや高性能トランジスタの研究・開発を行っています.強磁性体によってソースとドレインを構成したスピンMOSFETと呼ばれるデバイスは,電子のスピンを利用した情報の不揮発記憶が可能な高機能トランジスタです.これを用いることでCMOSロジックシステムの低消費電力化に有用な回路を構成することができます.このスピンMOSFETを実現するためにシリコンチャネルへスピンを注入する技術の開発などを進めています.また,圧電体ゲートとピエゾ抵抗チャネルを用いたピエゾエレクトロニックトランジスタ(PET)と呼ばれる高性能トランジスタの研究を進めています.これはピエゾ抵抗チャネルの金属-絶縁体転移を圧電体ゲートで制御することで,低リークでしかも0.1~0.2V程度の超低電圧で極めて高い電流駆動能力を実現できる究極のロジックデバイスとなる可能性があります.新型のPETを提案して,その設計方法やメモリ,ロジックなどへの回路応用などにつて研究・開発を進めています.